A unique approach to AI inference acceleration

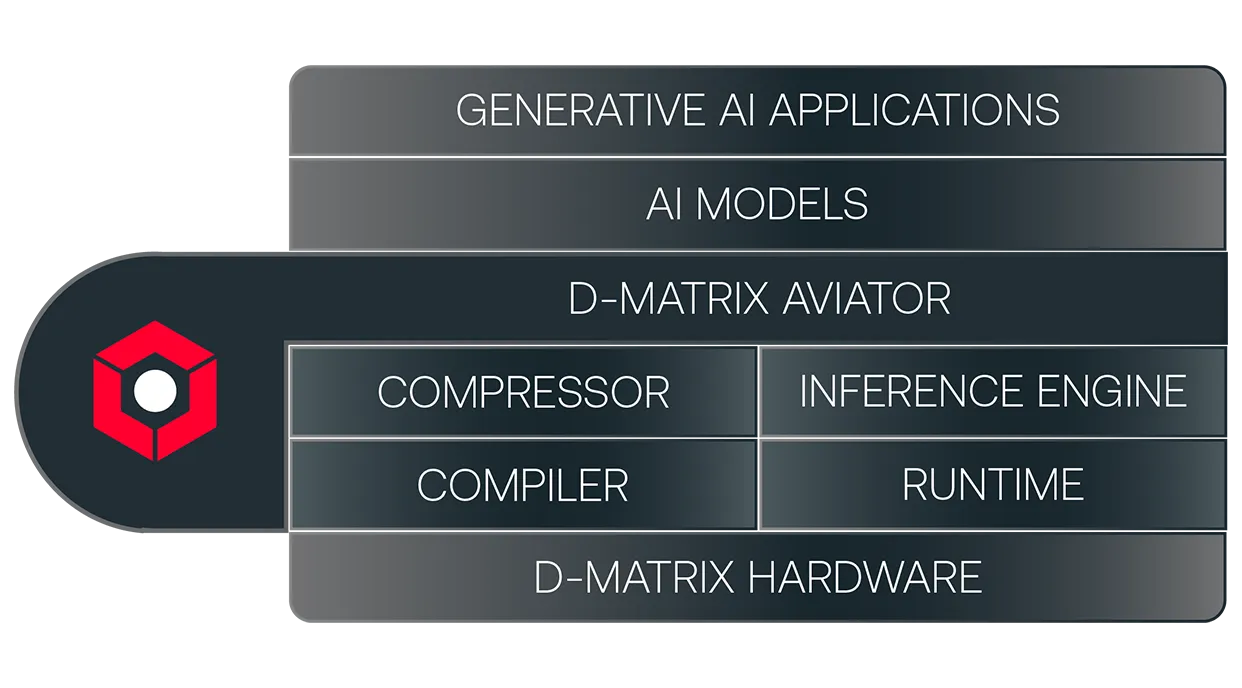

d-Matrix delivers world-first innovations in silicon, software, chiplet packaging and interconnects to create a one-of-a-kind inference compute platform efficiently runs modern workloads.

Next generation memory scaling with 3DIMC™

Introducing a breakthrough stacked DRAM technology. Scale up operations to larger models and millions of users with the same ultra low-latency experience.

Learn MoreCircuits

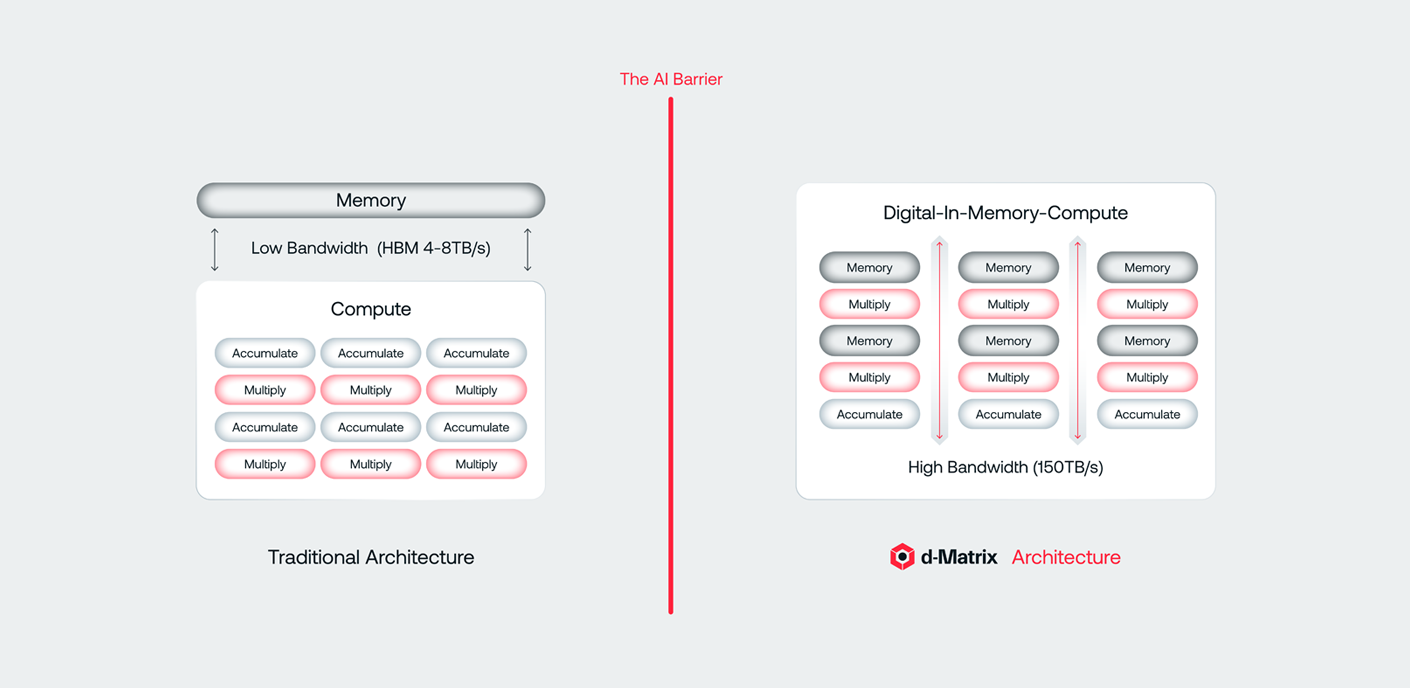

World’s first Digital In-Memory Computing (DIMC) solution that tightly integrates compute and memory to eliminate bottlenecks associated with traditional architectures

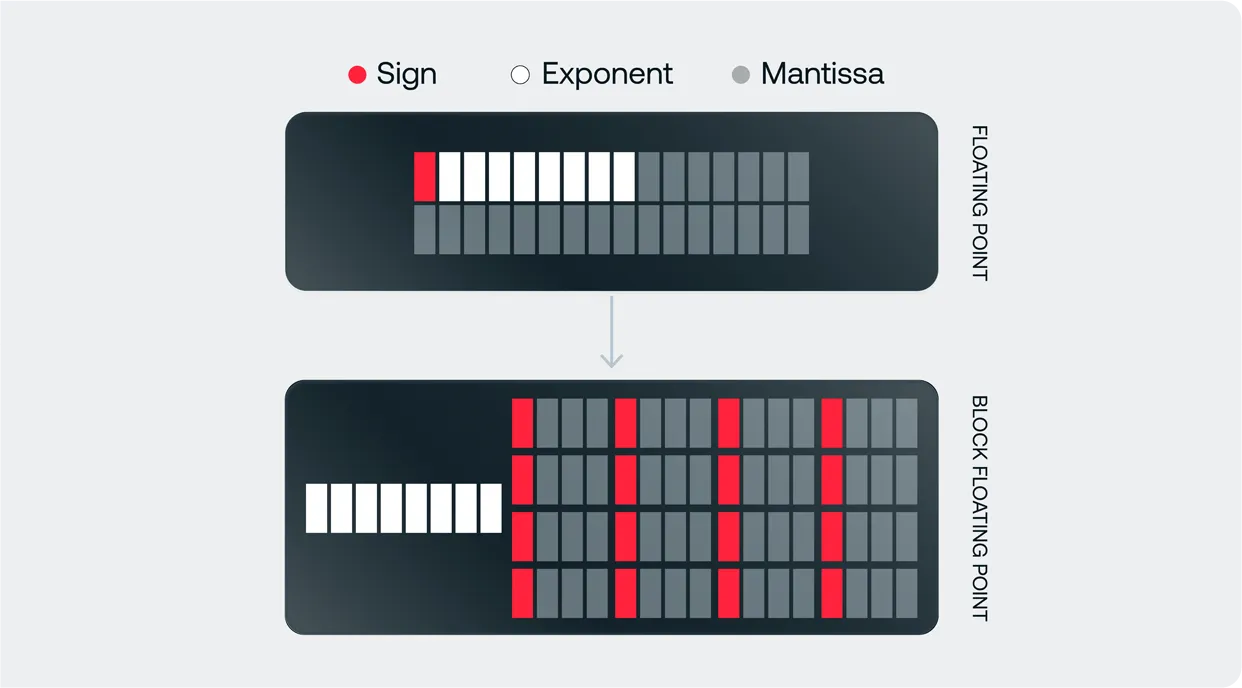

Numerics

Among the first to natively implement Block Floating Point numerics, offering the energy efficiency of integer arithmetic with the high dynamic range of floating-point.

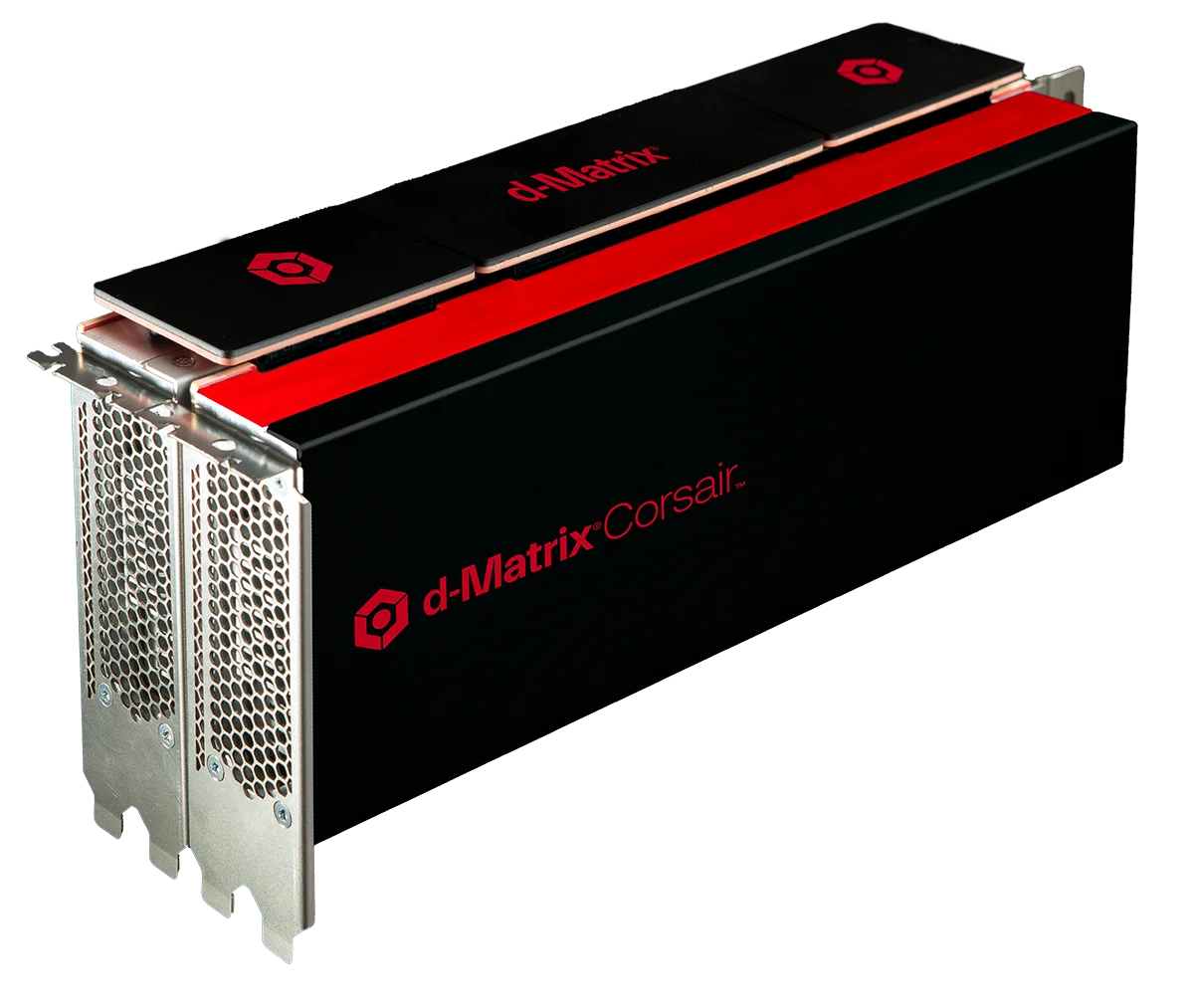

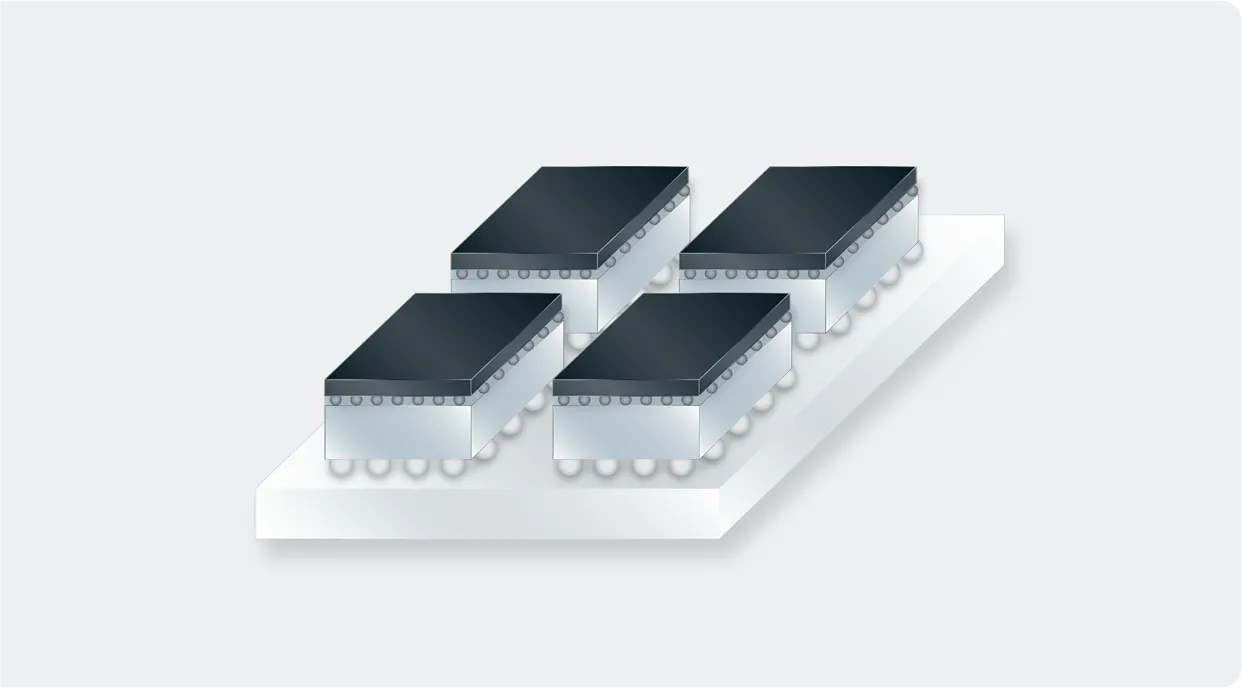

Chiplets & Packaging

Chiplet based architecture scales memory-compute complex using innovative die-to-die interconnects in an all-to-all topology and with advanced 2D/3D packaging

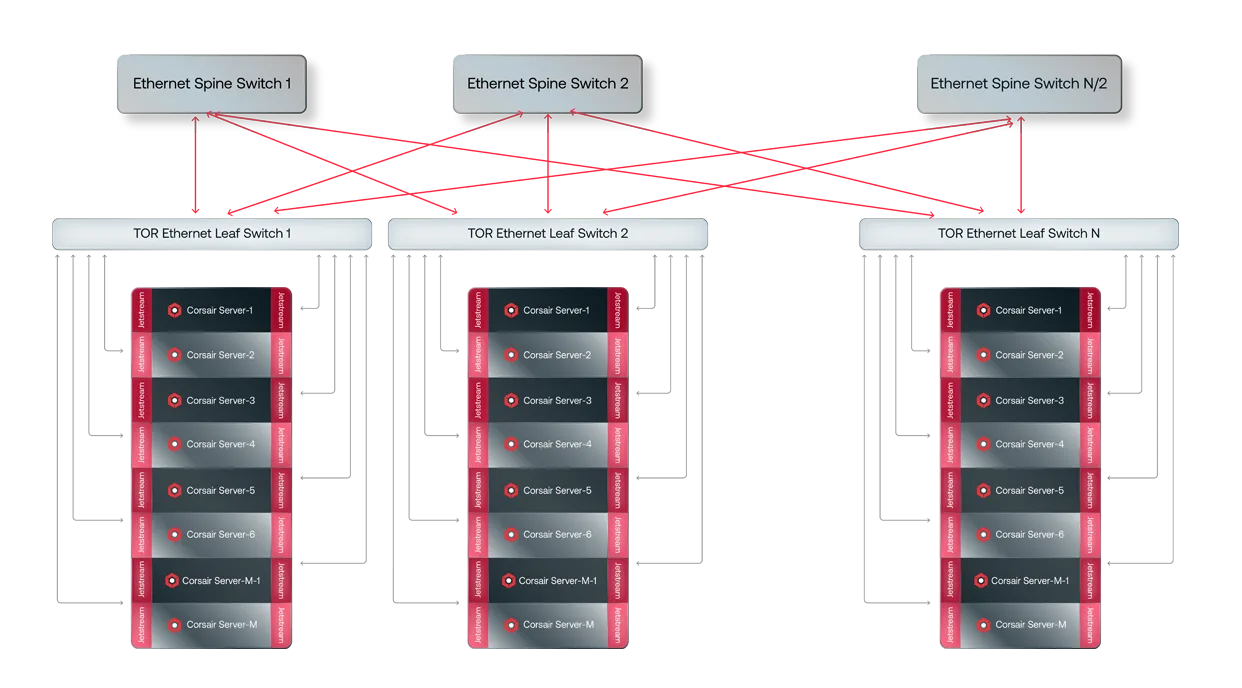

Scale-up and Scale-out

High bandwidth and fully connected topology up to 16 chiplets across 2 cards. Standard PCIe based scale-up within a node. Scale-out across nodes using PCIe or Ethernet.

Hardware-Software Codesign

Built with open software such as PyTorch, MLIR, Triton DSL. Programming models for spatial architectures and multi-level memory hierarchies, efficient networking communication between devices and minimal host synchronization